### Elettra Sincrotrone Trieste

# ESS WS control system development status

NSTEM CA

**Introduction - 1**

Software is just a tool that lets you to shift a task from the conceptual side (model) to the computing side (practical implementation of the model)

Head first: before coding anything define a model describing what you want to be performed by an automatic system

Defining a good (enough) model is a complex task that requires to identify the input, the output and the action (transfer function) that have to be performed in order to reach a goal

#### goal

#### measuring the transverse beam density profile by WS

DNVG

#### what is a WS

WS: an electro-mechanical device which measures the transverse beam density profile in a particle accelerator by means of a moving thin wire (CERN) WS input: signal generated by a moving wire (wire: primary sensing element)

WS output: transverse beam density profile

> beam density profile = f(wire position, time, ...)

#### main SW goal

to implement f() by the identification, development and connection of suited functional blocks that can be built by code

STEM CA

#### **Introduction - 3**

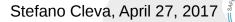

#### **Expected input pulse (theoretical shape)**

- → per channel;

- > per mechanical position;

- synchronized by timing system;

STEM CA

DNV·GI

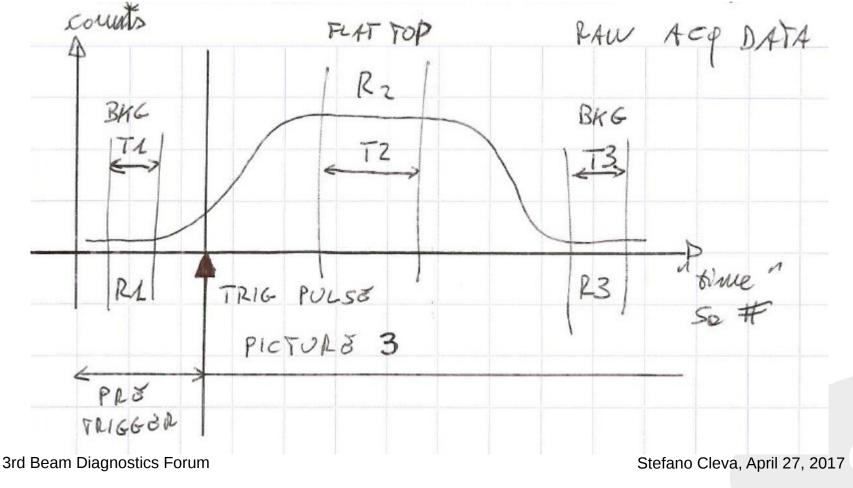

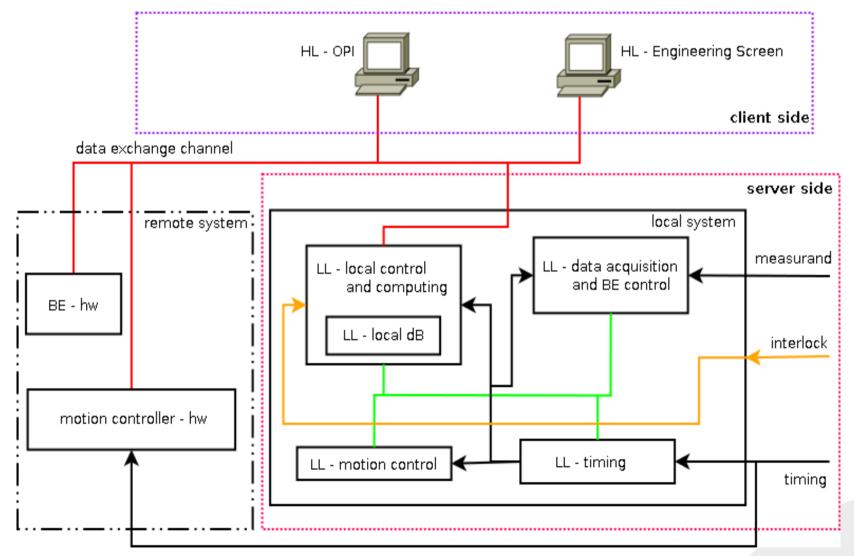

### WS conceptual HW layout suggests a two layers client/server SW architecture

STEM CERS

100 000

STEM CER,

DNV.GL

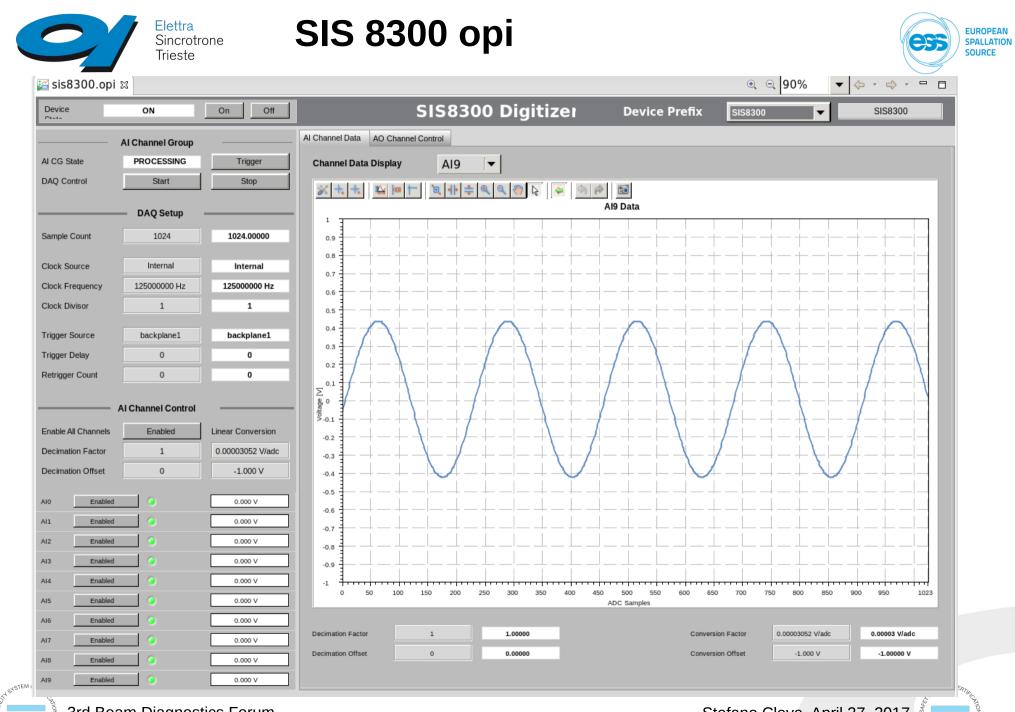

#### **Two layers SW architecture**

The high level layer (client side) is in charge of human interaction activities (control panel (OPI) and Engineering Screen)

The low level layer (server side) is in charge of all kind of HW access (device driver) and the logical functionality strictly related to the implementation of the WS transfer function

Ancillary low level tasks are protection and servicing

Constrain: EPICS based

#### **Expected SW functions – raw estimation**

Motion control: scan "trajectory" (step/fly mode) synchronized with the timing system Data acquisition synchronized with the timing system Elaboration of the acquired raw data accordingly to specified algorithms Data presentation Data archiviation Auto and procedure driven testing Data exchange (communication protocols – CA, TCP/IP, Ethercat, ...) State management (normal operation, alarms, ...) Local control HL: HMI

#### **Putting all together: tasks/functions**

3rd Beam Diagnostics Forum

NSTEM CF.

DNV.GI

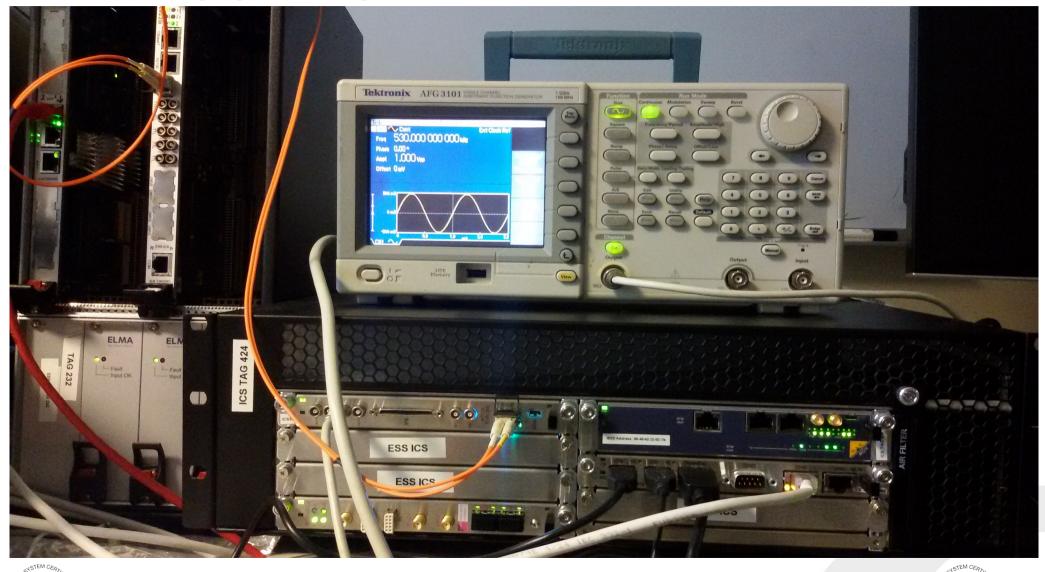

#### **Real equipment by ESS**

3rd Beam Diagnostics Forum

10

DNV.GL

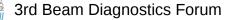

#### **HW components**

#### VME crate

- → CPU board;

- → EVG board;

#### **MicroTCA crate**

- → CPU board (i7);

- → EVR board;

- Struck 8300 L2 board (digitizer);

JSTEM CA

DNV·GI

#### Timing OPI - 1

|                |              |               |           |               |              | MRFI        | DC2 EVR | Dev      | ice Prefix | EVR-MTCA |   | -        | EVR-MTCA |                                 |

|----------------|--------------|---------------|-----------|---------------|--------------|-------------|---------|----------|------------|----------|---|----------|----------|---------------------------------|

| Platform Fi    | irmware Soft | ware Position | Pulsers O | utputs Presca | alers Inputs | Events      |         |          |            |          |   |          |          |                                 |

| mTCA 0         | 0x207 2.7.   |               |           |               |              | Width       |         |          | Delay      |          |   | Prescale | er       | Mapped events<br>Trig Set Reset |

| Enable         | ٠            |               | 💽 Pul0    | Active High   | 1000.000 us  | 1000.001 us | 88052   | 0.000 us | 0.000 us   | 0 cnts   | 1 | 1        | 11 ns    | 14 Disce Disco                  |

| Rx Error       | 0 Cnt        | 0 Cnt/10s     | 💽 Pull    | Active High   | 0.020 us     | 0.023 us    | 2       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 1        | 11 ns    | 4 Disco Disco                   |

| FIFO HW overf  | flc 893      |               | 💽 Pul2    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 1        | 11 ns    | Disce Disce Disco               |

| FIFO SW overr  | a 1225677    |               |           | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 1        | 11 ns    | Disce Disce Disco               |

| Interrupts     | 1227114      | 282 Hz        | 💽 Pul4    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

|                |              |               | 💽 Pul5    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| FIFO Event     | 1136336969   | 75740 evt/s   | 💽 Pul6    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| FIFO Loop      | 977462512    | 281 Hz        | 💽 Pul7    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| FIFO Capacity  | 53 %         |               | 💽 Pul8    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| Fraq Synth Loo | ck 🥥         |               | 💽 Pul9    | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| PLL Lock       | ۲            |               | 💽 Pul10   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| PLL Bandwidth  | n ML         | ML            | 💽 Pul11   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

|                |              |               | 💽 Pul12   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

|                | ——— Link ——  |               | 💽 Pul13   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| Status         | ۲            |               | 💽 Pul14   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| Speed          | 88.052 MHz   | 88.052 MHz    | 💽 Pul15   | Active High   | 0.000 us     | 0.000 us    | 0       | 0.000 us | 0.000 us   | 0 cnts   | 1 | 0        | 11 ns    | Disce Disce Disco               |

| Clock Error    | 0.552 KHz    |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Clock Period   | 1.136E-8 s   |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Timeout        | 0            |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| meoue          |              |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

|                | ——Time ——    |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Time Valid     | ۲            |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Time Src       | Event clock  |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Clock          | 0.000 MHz    | 88.052 MHz    |           |               |              |             |         |          |            |          |   |          |          |                                 |

| Clock prescale | er 1         |               |           |               |              |             |         |          |            |          |   |          |          |                                 |

Time

DNV.GL

SO 9001

Stefano Cleva, April 27, 2017

12

DNV-GL

#### Timing OPI - 2

#### 🗩 🗉 CS-Studio (on dev-sc-01) File Edit Search CS-Studio Window Help 📑 🔝 🖾 - 🔌 🔌 📑 🥂 🕁 - 🔯 🔗 -😭 🛛 🔛 ▼ | → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → → € € 100% 🚰 TTmrfioc2Evr.opi 😫 Pulsers Outputs Prescalers Inputs Events Position Platform Firmwar Software 2.7.13 0x207 8:0.0 mTCA Soft Event **Rx** Counter Enable Event0 Disconnecte Disconnected Event1 Disconnecte Disconnected **Rx Error** 0 Cnt 0 Cnt/10s Event2 Disconnecte Disconnected FIFO HW overf 1213 Event3 Disconnecte Disconnected FIFO SW overr 8670099 8670205 Event4 4 Interrupts 8672178 279 Hz Event5 Disconnecte Disconnected **FIFO Event** -1151090312 75299 evt/s Event6 Disconnecter Disconnected FIFO Loop 984907127 280 Hz Disconnecte Disconnected Event7 FIFO Capacity 53 % Event8 Disconnecte Disconnected Frag Synth Loc Event9 Disconnecte Disconnected Event10 Disconnecte Disconnected PLL Lock Event11 Disconnecte Disconnected PLL Bandwidth ML ML Event12 Disconnecte Disconnected Link Event13 Disconnecte Disconnected Event14 14 31084 0 Status Disconnecter Disconnected Event15 Speed 88.052 MHz 88.052 MHz Event16 Disconnecte Disconnected Clock Error 0.552 KHz Event17 Disconnecte Disconnected Clock Period 1.136E-8 s Event18 Disconnecte Disconnected Timeout 0 Disconnecte Disconnected Event19 Event20 Disconnecte Disconnected -Time Event21 Disconnecte Disconnected Time Valid Event22 Disconnecte Disconnected Time Src Event clock Disconnecte Disconnected Event23 Clock 0.000 MHz 88.052 MHz Event24 Disconnecte Disconnected Clock prescale 1 Event25 Disconnecter Disconnected Time Even+26 -SYSTEM (

iocuser

DNV.GI

150 900

3rd Beam Diagnostics Forum

DNV.GL

**3rd Beam Diagnostics Forum**

DNV.GL ISO 9001

Stefano Cleva, April 27, 2017

DNV.GL

#### **EPICS IOC**

#### LL local control runs as EPICS IOC

STEM CEA,

DNV.GL

#### **PVs - 1**

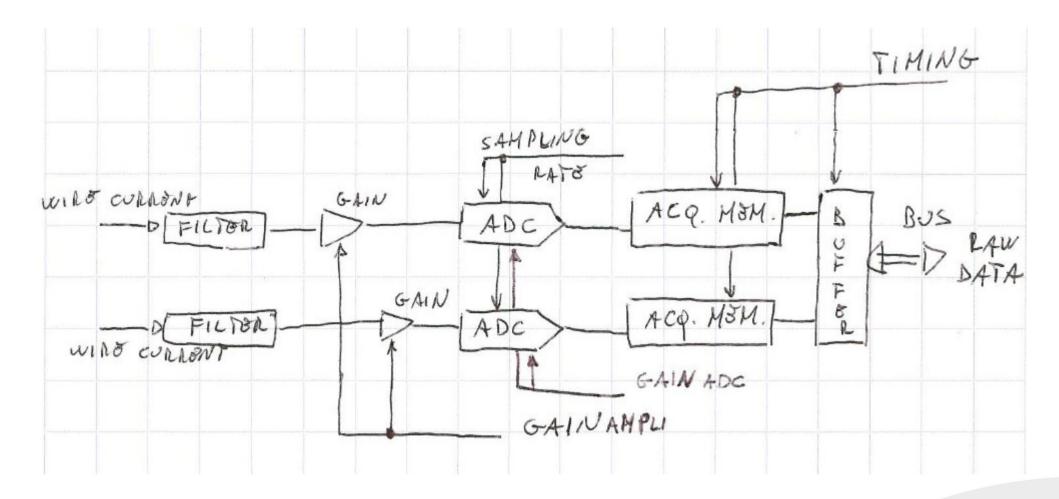

1 wire generates 2 Analog Input signals (measurand) that are acquired by 2 ADCs:

- Iow gain wide range raw current;

- high gain small range raw current;

Interlock signal: digital input

Timing signal: digital input

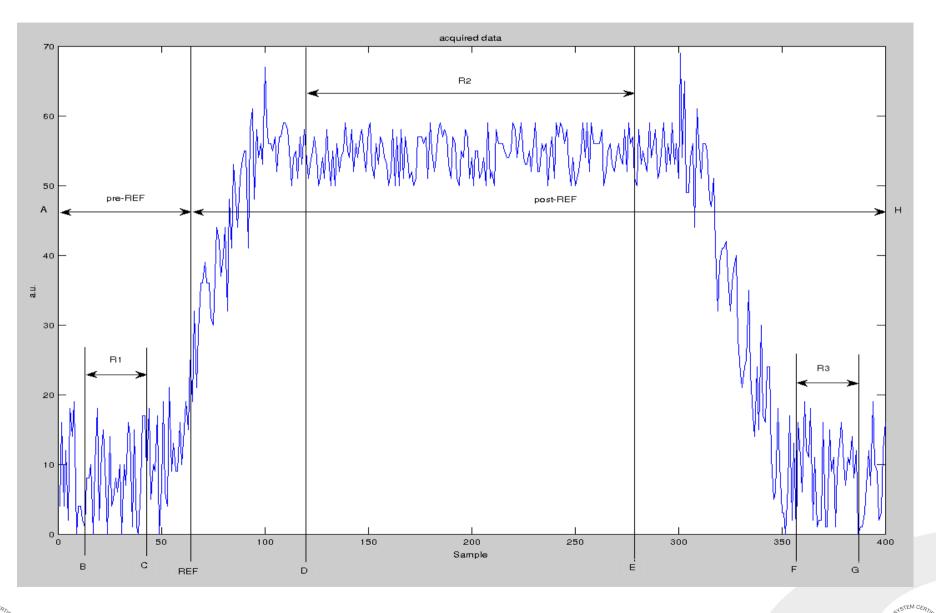

Waveform output: beam shape, obtained following one ore more assigned data processing algorithms that define the transfer function

DNVO

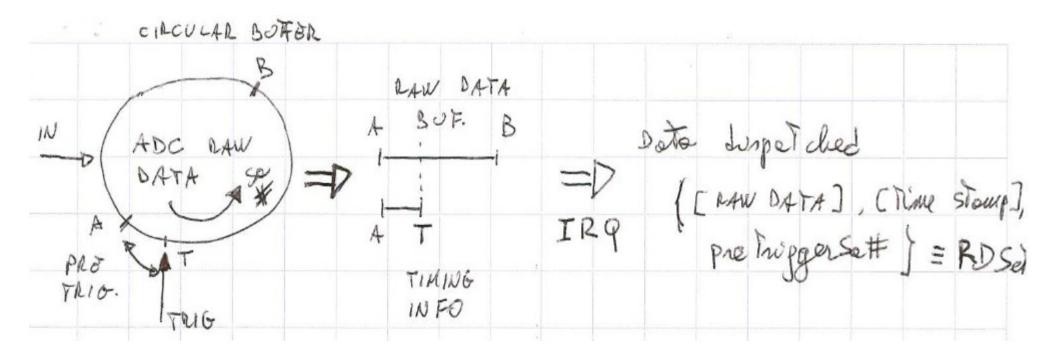

#### **Sampling and Timestamping**

NSTEM CA

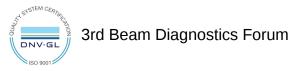

## SW + EPICS – 4: Pulse shape (simulated)

3rd Beam Diagnostics Forum

Stefano Cleva, April 27, 2017

18

DNV.GL

#### **PVs - 2**

Controlled remote "Analog" Outputs:

- → AFE amplifiers gain (set by ethernet messages sent to BE);

- → AFE HVPS set point (set by ethernet messages sent to BE);

- Wire position, 1 or 2 axis (set by ethernet messages);

Acquired remote "Analog" Inputs:

→ Wire position (encoders), 1 or 2 axis (get by ethernet messages);

Limit Switches (get by ethernet messages);

20

STEM CEA

DNV.GL

#### **BE: protocol file**

Terminator = CR;

ReadStatus { out "RS?"; in "%s"; ExtraInput = Ignore; }

SetBits { out "SB:%s"; in "%{OK|KO}"; ExtraInput = Ignore; }

```

ReadBits {

out "RB?";

in "%s";

ExtraInput = Ignore;

}

```

ReadVoltage { out "RV?"; in "%s"; ExtraInput = Ignore;

ReadTemp { out "RT?"; in "%s"; ExtraInput = Ignore;

SetVoltage { out "SV:%s"; in "%{OK|KO}"; ExtraInput = Ignore; } Abort { out "AB"; in "%{OK|KO}"; ExtraInput = Ignore; }

Unsupported { out "fc"; in "%s"; ExtraInput = Ignore; }

```

get_IDN {

out "*IDN?";

in "%s";

ExtraInput = Ignore;

}

```

STEM CA

#### **BE: protocol simulation**

Example: status readback SETVOLTAGE:READVOLTAGE:BITS:SWVERSION: SWTYPE:BESTATUS:CHECK\_DIGIT

reply = str(counter) + ':' + str(counter - 100) + ':' + str(counter + 40) + ':' + '1234' + ':' + '1' + ':' + 'R' + ':' + str(counter1) + '\r'

SWTYPE : 1 = WS 5=SCINT

#### **PVs - 3**

Several auxiliary PVs are foreseen in order to fully control the WS acquisition system:

- ADCs gain (if required/available);

- → System integrity detection signals (e.g. dark current, wire integrity, ...);

- System integrity auto testing signals (simulated inputs);

- SW generated triggers and interlocks;

→

24

SYSTEM CEA

DNV.GI

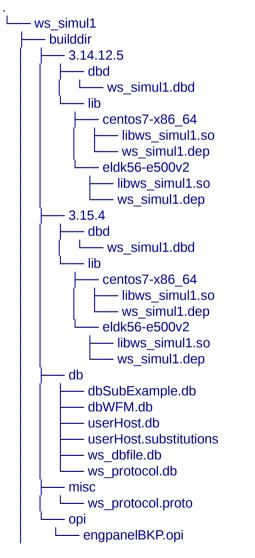

#### **Current IOC module development status**

**3rd Beam Diagnostics Forum**

Stefano Cleva, April 27, 2017

STEM CEAN

DNV.GL

#### **Current IOC module development status**

– db dbSubExample.db dbSubExample.db~ - dbWFM.db dbWFM.db~ - userHost.substitutions userHost.substitutions~ user.substitutions~ - wd dbfile.db~ - ws dbfile.db - ws dbfile.db~ - ws protocol.db - ws protocol.db~ - doc - Makefile - misc - opi engpanelBKP.opi - protocol - ws protocol.proto -ws protocol.proto~ - src - dbSubExample.c - dbSubExample.c~ - dbSubExample.dbd – dbSubExample.dbd~ — initTrace.c — initTrace.dbd - startup - test

STEM CEAN

DNV.GL

#### **EPICS** integration

#### **Signal Processing**

Several measurement procedures and models to be fit to the acquired data are foreseen in order to compute the beam profile;

Data acquisition auto switching between channels (HG vs LG);

#### **Local Protection System**

Its primary function should be to avoid damages generated by user actions: several details have to be defined

#### **Scanning Logic and Motion Control**

Several details have to be defined

The global picture describing the SW is now clear enough to develop the first release (NON Real-Time) of the controlling code of the WS and it's OPI.

Thanks to the availability of the real HW the porting of the original simulated code/IOC has been ported to reality but...

... a lot of details have to be still investigated, depending on:

→ HW issues (e.g. motion controller driving, real time approach to the buffer acquisition and storage, ...);

→ Low level drivers issues (motion controller and its EPICS demo ioc);

- OPI and Engineering screen definitions;

- Code porting to Real Time operation issues;

GIGIEM CERTING MICH

→